- 您现在的位置:买卖IC网 > Sheet目录1203 > COREPCIF-RM (Microsemi SoC)IP MODULE COREPCIF

�� �

�

�

�Actel� has� an� allocated� Vendor� ID� that� CorePCIF� customers� may� use,� and� Actel� will� allocate� a� unique� Device� ID� when�

�the� Actel� Vendor� ID� is� used.� Actel� will� allocate� unique� subsystem� Vendor� IDs� on� request.� Contact� Actel� Technical�

�Support� (tech@actel.com� )� for� more� information.�

�The� capability� pointer� is� used� to� point� to� the� CorePCIF� vendor� capability� data,� and� also� to� the� hot-swap� capability,� if�

�enabled.� The� capability� list� structure� varies,� depending� on� the� core� configuration.�

�Read/Write� Configuration� Registers�

�The� following� registers� have� at� least� one� bit� that� is� both� read-� and� write-capable.� For� a� complete� description,� refer� to� the�

�appropriate� table.�

����?� I/O� Base� Address� Register� Bit� Definition� (� Table� 7-9� on� page� 110� )�

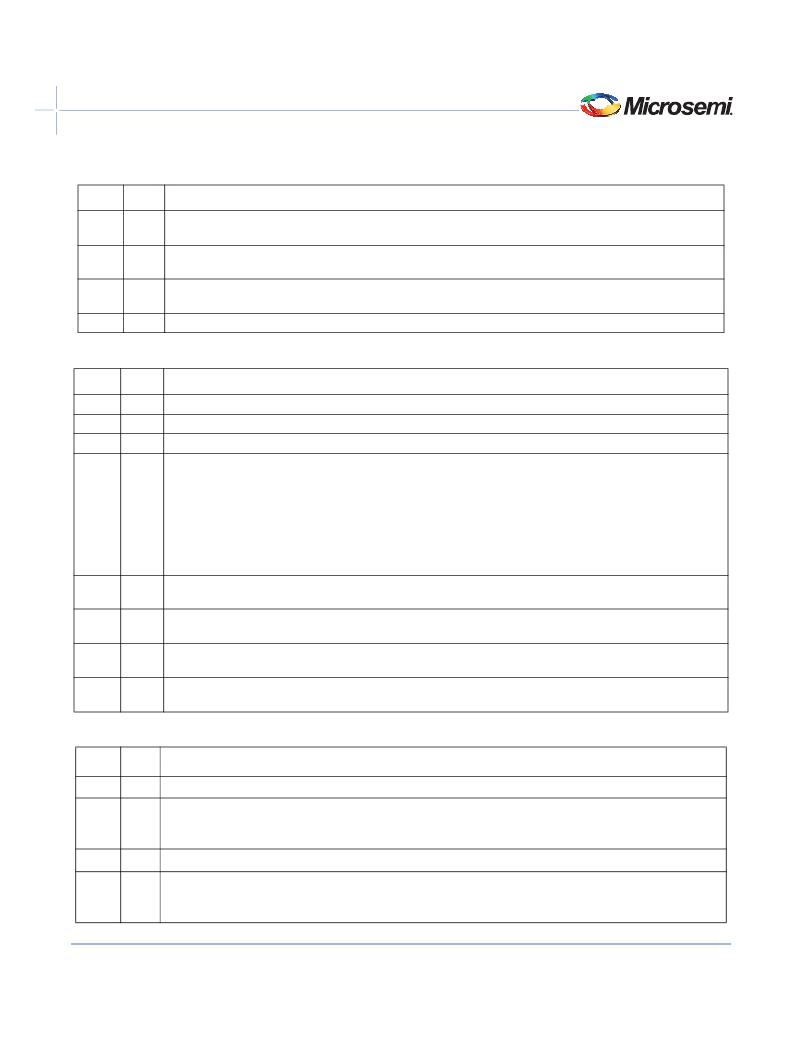

����Table� 7-6� ·� Command� Register� 04� Hex�

�Bit(s)�

�0�

�1�

�2�

�3�

�4�

�5�

�6�

�7�

�8�

�9�

�10�

�15:11�

�108�

�Type�

�RW�

�RW�

�RW�

�RO�

�RO�

�RO�

�RW�

�RO�

�RW�

�RO�

�RW�

�RO�

�Description�

�I/O� Space�

�A� value� of� 0� disables� the� device's� response� to� I/O� space� addresses.� Set� to� 0� after� reset.�

�Memory� Space�

�A� value� of� 0� disables� the� device's� response� to� memory� space� addresses.� Set� to� 0� after� reset.�

�Bus� Master�

�When� set� to� 1,� this� bit� enables� the� macro� to� behave� as� a� PCI� bus� Master.� For� Target-only� implementation,� this� bit� is�

�read-only� and� is� set� to� 0.�

�Special� Cycles�

�Response� to� special� cycles� is� not� supported� in� the� core.� Set� to� 0.�

�Memory� Write� and� Invalidate� Enable�

�Memory� Write� and� Invalidate� Enable� is� not� supported� by� the� core.� Set� to� 0.�

�VGA� Palette� Snoop�

�Assumes� a� non-VGA� peripheral.� Set� to� 0.�

�Parity� Error� Response�

�When� 0,� the� device� ignores� parity� errors.� When� 1,� normal� parity� checking� is� performed.� Set� to� 0� after� reset.�

�Wait� Cycle� Control�

�No� data-stepping� supported.� Set� to� 0.�

�SERRN� Enable�

�When� 0,� the� SERRN� driver� is� disabled.� Set� to� 0� after� reset.�

�Set� to� 0.� Only� fast� back-to-back� transactions� to� the� same� agent� are� allowed.�

�Interrupt� Disable�

�When� set,� this� prevents� the� core� from� asserting� its� INTAn� output.� This� bit� is� set� to� 0� after� reset.�

�Reserved.� Set� to� '00000'.�

�v4.0�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

COREU1LL-AR

IP MODULE COREU1LL

COREU1PHY-AR

IP MODULE COREU1PHY

CORR-8BIT-XM-UT2

SITE LICENSE IP CORRELATOR XP

CP2-GSA-L

CONN SHIELD LOWER TYPE A 22

CP2-HSA110-1

CONN SHROUD CPCI 2MM TYPE A 22

CP2-HSC055-4

CONN SHROUD CPCI 2MM TYPE C 11

CP2-K3567-SR-F

COMPACT PCI - MISC

CP2105EK

KIT EVAL FOR CP2105

相关代理商/技术参数

COREPCIF-RMFL

功能描述:IP MODULE 制造商:microsemi corporation 系列:- 零件状态:在售 类型:许可证 应用:- 版本:- 许可长度:- 许可 - 用户明细:- 操作系统:- 配套使用产品/相关产品:Microsemi 器件 媒体分发类型:- 标准包装:1

COREPCIF-UR

功能描述:HW/SW/OTHER 制造商:microsemi corporation 系列:* 零件状态:在售 标准包装:1

COREPCI-SN

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-SR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-UR

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPCI-XX

制造商:ACTEL 制造商全称:Actel Corporation 功能描述:CorePCI v5.41

COREPRO LEDBULB 10.5-60W B

制造商:Philips Lumileds 功能描述:

COREPRO LEDBULB 10.5-60W E

制造商:Philips Lumileds 功能描述: